从芯片到系统 数据处理与存储核心硬件技术全景解读

在现代信息技术体系中,数据处理与存储服务构成了数字世界的基石。支撑这些服务的是一系列功能各异、定位不同的硬件核心。从通用计算到专用加速,从简单控制到复杂决策,不同的芯片架构在数据处理与存储的生态链上扮演着独特的角色。理解这些核心硬件的特性和应用场景,对于构建高效、可靠的信息系统至关重要。

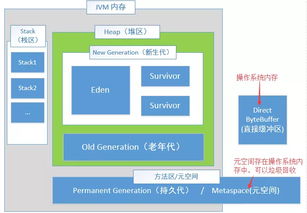

通用处理器构成了计算体系的广泛基础。中央处理器(CPU)作为通用计算的核心,以其强大的逻辑控制和顺序指令执行能力,成为各类计算设备的大脑,负责运行操作系统、调度任务和执行通用应用程序。图形处理器(GPU)则凭借其高度并行化的流处理器架构,在图形渲染、科学计算和人工智能训练等需要大规模并行计算的领域展现出巨大优势。而通用处理器(GPP)是一个更宽泛的术语,涵盖了包括CPU在内的各类可编程处理器,强调其软件定义功能的灵活性。

嵌入式与控制系统依赖一系列专用或微型的计算单元。微控制器(MCU)集成了处理器核心、内存和外围接口于单一芯片,常用于对功耗、成本和尺寸敏感的嵌入式控制场景,如家电、传感器节点等。微处理器(MPU)通常指更强大的处理器核心,需要外接内存和外围芯片,用于更复杂的嵌入式系统,如工业控制器、高端物联网网关。在汽车电子领域,电子控制单元(ECU)并非单一芯片,而是指集成了微控制器、传感器、执行器接口和特定控制软件的完整嵌入式系统模块,负责控制发动机、刹车、车窗等具体功能。

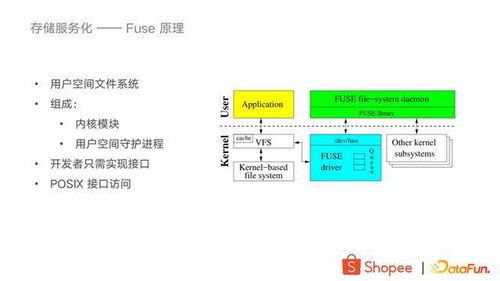

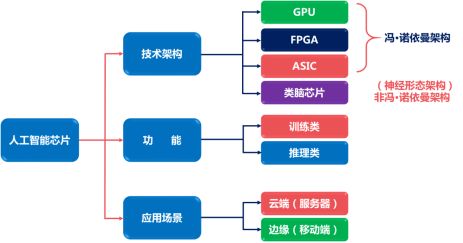

专用与可编程硬件为特定任务提供优化加速。片上系统(SoC)将CPU、GPU、内存控制器、DSP、各种接口(如USB、PCIe)乃至专用AI加速核等多个功能模块集成在一块芯片上,实现了高性能、低功耗和小型化,是现代智能手机、平板电脑和许多物联网设备的“心脏”。数字信号处理器(DSP)针对数字信号处理算法(如滤波、编解码)进行了高度优化,在通信、音频、图像处理等领域不可或缺。现场可编程门阵列(FPGA)提供了一种硬件可重构的解决方案,用户可以通过编程定义其内部逻辑电路,在需要高吞吐量、低延迟且算法可能变更的场合(如原型验证、通信基站加速)非常有用。专用集成电路(ASIC)则是为特定应用量身定制的芯片,一旦流片,功能固定,在量产规模下能提供极致的性能、功耗和成本优势,例如比特币矿机芯片、手机中的神经网络处理单元(NPU)。

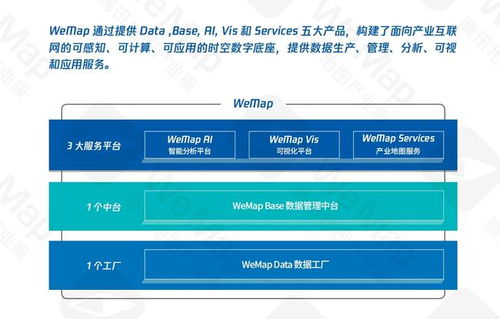

所有这些硬件技术的价值,最终都通过“数据处理和存储服务”这一上层建筑得以体现。数据处理服务涵盖了从原始数据采集、清洗、转换、分析到可视化的全过程,其效率与准确性直接依赖于底层CPU、GPU、FPGA、ASIC等硬件的算力支撑。存储服务则负责数据的持久化保存与高速读写,虽然本文聚焦处理芯片,但存储服务与处理单元通过高速总线(在SoC中更是紧密集成)协同工作,构成了完整的数据生命周期管理闭环。例如,一个智能驾驶系统:MCU/ECU负责实时控制车辆执行机构,SoC(内含CPU、GPU、DSP、NPU)运行感知与决策算法,处理来自传感器的海量数据,而整个过程需要与存储服务(内存、闪存)频繁交互以存取地图、模型和临时数据。

从通用灵活的CPU、GPP,到并行高效的GPU,再到集成度高的SoC和MCU,以及专用加速的DSP、FPGA、ASIC,最后到实现具体功能的ECU,这些硬件构成了一个层次分明、协同工作的技术谱系。它们共同支撑起从云端大数据分析到边缘实时控制、从消费电子到工业自动化等广泛领域的数据处理与存储服务。未来的发展趋势将是进一步融合——SoC中集成更多专用加速单元,异构计算架构(CPU+GPU+ASIC)成为常态,软硬件协同设计以更高效地满足日益复杂和多样化的数据处理需求。

如若转载,请注明出处:http://www.52animal.com/product/43.html

更新时间:2026-04-16 00:05:34